Verilog Code For Serial Adder Circuit

I have to implement a circuit that performs A+B+C+D serially. A and B are added using the first adder, the result is added to C using the second adder and finally the result is added to D using the third adder, one after the other. The problem is, in order to make the design low power. I have to turn off the other two adders which are not in use.

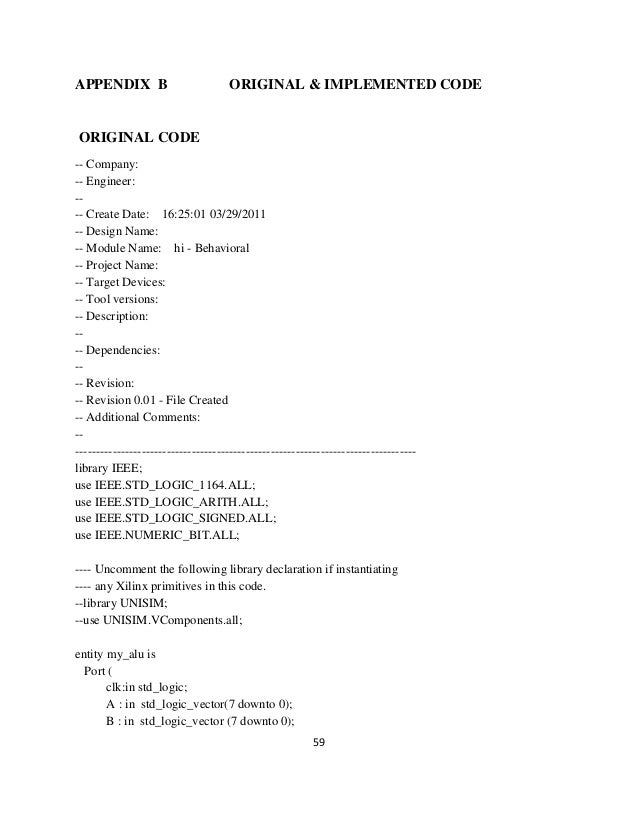

7 Design an 8-bit RWM cell with bidirectional data bus and synthesize the design using the synthesis tool. 8 Design an 8-bit ALU which performs eight basic arithmetic and logic operations and maintains a Flag register. 9 Design a 4-bit Bit-Serial adder in Verilog HDL, simulate it and synthesize using the synthesis. Verilog code for Full Adder, Full Adder in Verilog, Adder Verilog, Full adder Verilog, Full adder Verilog code, verilog code full adder Verilog code for Full Adder - FPGA4student.com Home. I need to make a 4 bit full adder using verilog can anybody please help me? Verilog code and circuit details here Verilog rtl code for full-adder.

All I can think is Enable and Disable signals, but this causes latency issues. How do I synthesize this in in an effective manner in verilog? A,B,C,D may change every clock cycle. A start signal is used to indicate when a new calculation is required.

I assume your adder has been implied via sum = A + B. For area optimisation why do you not share a single adder unit. A+B in CLK1, SUM+C in CLK2, SUM+D in CLK3. Then you have nothing to disable or clock gate.

The majority of power is used when values change, so zeroing inputs when not used can actually increase power by creating unnecessary toggles. As adders are combinatorial logic all we can do to save power for a given architecture is hold values stable, this could be done through the use of clock gate cells controlling/sequencing input and output flip-flops clks. Update With the information that a new calculation may be required every clock cycle, and there is an enable signal called start. Th question made reference to adding them serially ie: sum1 = A + B; sum2 = sum1 + C; sum3 = sum2 + D; Since the result is calculated potentially every clock cycle they are all on or all off.

The given serialisation (which is all to be executed in parallel) has 3 adders stringed together (ripple path of 3 adders). If we refactor to: sum1 = A + B; sum2 = C + D; sum3 = sum1 + sum2; Or ripple path is only 2 adders deep allowing a quicker settling time, which implies less ripple or transients to consume power. I would be tempted to do this all on 1 line and allow the synthesis tool to optimise it.

Adder Verilog Code

Sum3 = A + B + C + D; For power saving I would turn on auto clock gating when synthesising and use a structure that worked well with this technique: always @(posedge clk or negedge rstn) begin if (rstn) begin sum3.

’ is not ' (notice the shape difference). Verilog works with the apostrophe character ( ', ASCII 0x27). Your ’ is likely an extended ASCII character. There is also a » character, which I believe should be! I'm guessing you wrote your code in word editor (ex Microsoft Word, LibreOffice Writer, Apple iWork, etc). These kinds of editors tend to swap ' for ’ while you type because it is more visually appealing for humans. Email clients and some messaging apps tend to do this too.

You should always write your code in a plain texted editor or an editor intended for writing code. Emacs and Vim are popular editors for writing code; syntax highlighting plugins are available for both. An IDE, like Eclipse, is another option. Notepad does work as well. I also noticed you used and assign statement on the reg type temp.

Verilog Full Adder Code

Software grafik barber johnson. This is not legal in verilog. Assign statements can only be done on net types (e.g. You may have other compiling errors that will show up after fixing ’ and », the error message will likely be more helpful.

Adder In Verilog

The compiler will not flag it, but recommend coding style is to use blocking assignments ( =) inside combination block ( always@(.)), not non-blocking (.